Startup Portfolio

Semiconductor AIのPartcl、AI駆動でチップ設計を高速化し開発サイクルの常識を刷新

AIを活用した次世代チップ設計プラットフォームのPartclが正式にローンチし、半導体開発のボトルネックとなってきたチップのコンパイル工程を抜本的に短縮する取り組みを打ち出しました。従来は数週間を要していたコンパイル時間を数分にまで短縮し、18〜24カ月に及ぶASIC(特定用途向け集積回路)の設計サイクルを大幅に圧縮することを目指します。

Partclは、物理法則を踏まえたシミュレーション、合成データ生成、GPUで加速されたアルゴリズムを組み合わせることで、エンジニアがチップを設計・検証・最適化する速度を飛躍的に高めます。これにより、電力・性能・面積(PPA)の見積もりが迅速化し、RTL段階での不具合修正や設計フィードバックのループが短くなります。AIアクセラレータ、IoTデバイス、モバイルSoCといった進化の速い分野で、厳しいテープアウト期限に対応するうえで重要な改善だとしています。

同社は、GPUネイティブに動作するよう物理設計ツールを一から再設計し、チップ速度や信頼性の向上といった性能面のブレークスルーを実現しました。創業者のVamshi Balanaga氏とWilliam Salcedo氏は、Nvidiaや初期段階のスタートアップでのエンジニア経験を通じ、従来ツールではシミュレーション待ちに何週間も費やした末、些細な文法やタイミングの誤りが見つかるといった非効率を目の当たりにしてきました。Partclは、そうした現場課題を解消するために構築されたとしています。

AIとチップ設計の橋渡しもPartclの特徴です。従来のEDAツールは、ドメイン特化データの不足からAI活用が進みにくい課題がありました。Partclは、物理ベースのシミュレーションから合成データを生成し、それを用いてAIモデルを学習させることで、より賢く迅速な設計判断を支援します。GPU加速を前提に設計されたツール群と、半導体設計ワークフローへの深い理解を背景に、Partclは半導体開発の在り方を再定義する存在になるとしています。

Partclについて

Partclは、AIとGPU加速を活用して半導体の物理設計と検証を高速化するチップ設計プラットフォームを提供するスタートアップです。物理法則に基づくシミュレーションと合成データ生成により、コンパイル時間を大幅に短縮し、PPA最適化や不具合修正の迅速化を実現します。AI時代に求められるスピードと反復性を備えたチップ開発環境の構築を目指しています。

関連ニュース

Partcl に興味がありますか?

最新ニュース

会議中にボットで文字起こししてノートを生成する"Granola"がSeries Cで$125Mを調達し評価額が$1.5Bに拡大

2026/03/26

医療システムと連携しAIの評価および導入を支援する"Qualified Health"がSeries Bで$125Mを調達

2026/03/26

自己免疫疾患に適応する多機能抗体を設計するAI抗体創薬のBiolojic Design、Teva提携下のTEV325で前臨床マイルストンを達成

2026/03/26

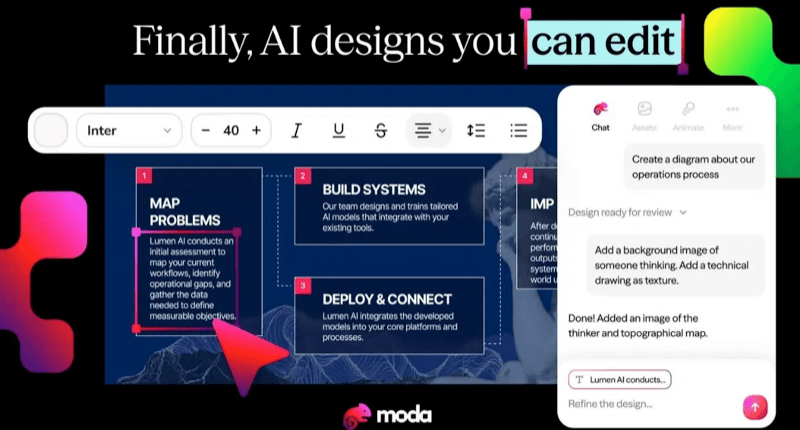

企業ブランドを深く理解した編集可能なデザインを作成するAIプラットフォームの"Moda"がSeedで$7.5Mを調達

2026/03/26

医療機関向けのRCM向けの主要なAIオーケストレーションプラットフォームの"Adonis"がSeries Cで$40Mを調達

2026/03/26